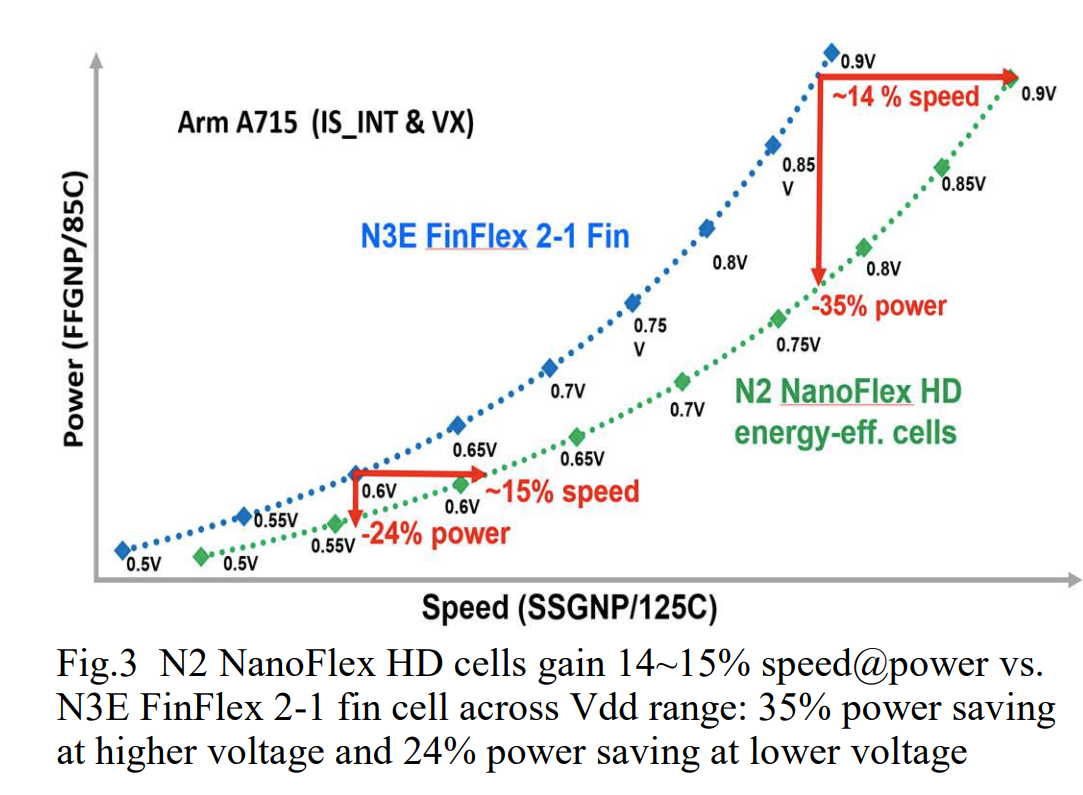

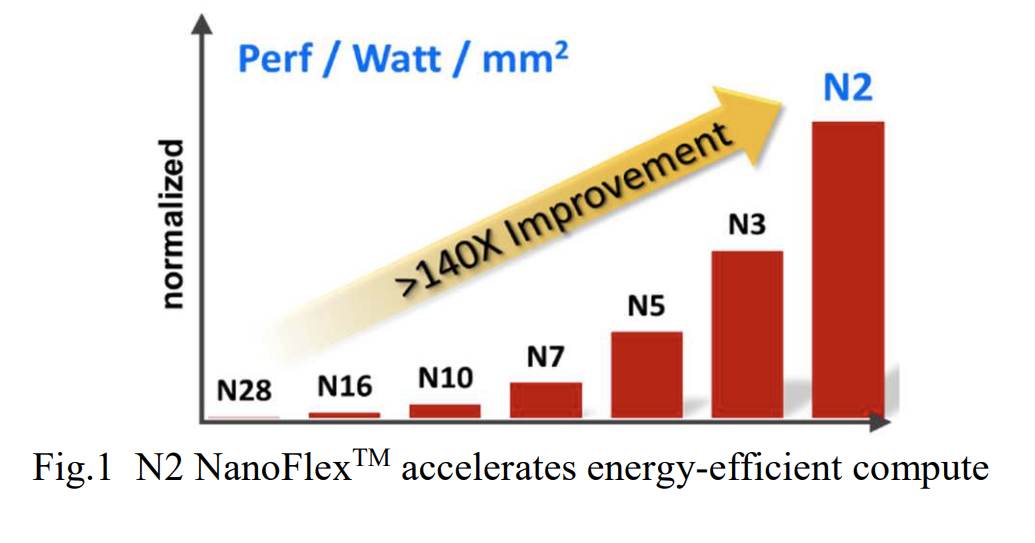

TSMC revealed more details about its N2 (2nm class) manufacturing process at the IEEE International Electron Device Meeting (IEDM) earlier this month. The new production node promises a 24 to 35% power reduction or a 15% power increase at the same voltage and 1.15 times higher transistor density than the previous generation 3nm process. The vast majority of these benefits are enabled by TSMC's new Gate All-Around (GAA) nanosheet transistors, along with the N2 NanoFlex design technology co-optimization capability and several other enhancements detailed at IEDM.

Gate-around nanosheet transistors allow designers to adjust their channel width to balance performance and power efficiency. Additionally, TSMC's N2 features N2 NanoFlex DTCO, allowing developers to design short cells with minimal area and improved power efficiency or large cells optimized for maximum performance. The technology also includes six voltage thresholds (6Vt) over a 200mV range, achieved through TSMC's third-generation dipole-based integration with n-type and p-type dipoles.

N2's innovations introduced at the process and device levels aim not only to increase transistor drive currents by improving sheet thickness, junctions, dopant activation and voltage engineering, but also to reduce effective capacitance (Ceff) by one achieve industry-leading energy efficiency. Taken together, these improvements result in I/CV speed gains of approximately 70% and 110% for N-type and P-type nanosheet transistors, respectively.

Compared to FinFETs, N2 nanosheet transistors deliver significantly better performance per watt at low supply voltage ranges of 0.5V to 0.6V, with process and device optimizations increasing clock speeds by approximately 20% and standby power consumption at 0.5V -Reduce operations by approximately 75%. Additionally, the integration of N2 NanoFlex and multiple threshold voltage options (Multi-Vt) enables additional design flexibility for power-efficient, high-logic-density processors.

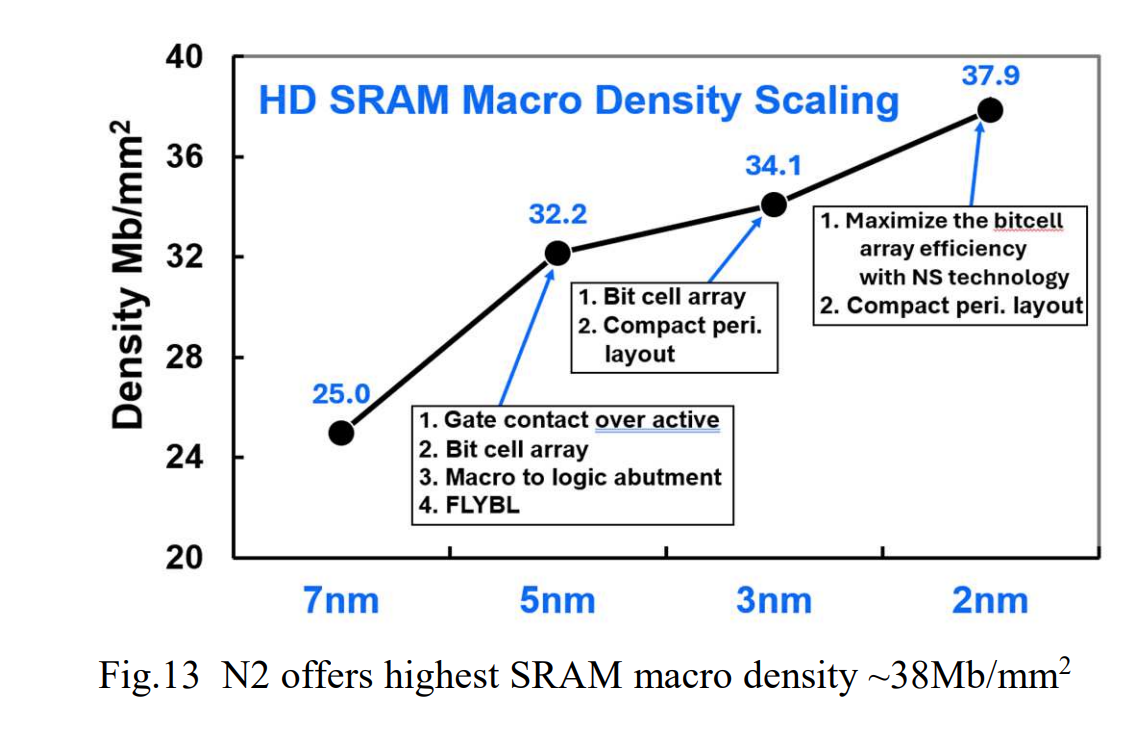

The advantages of the transistor architecture and DTCO directly impact SRAM scalability, which has been difficult to achieve with leading-edge nodes in recent years. With N2, TSMC has managed to achieve a record-breaking 2nm SRAM density of approximately 38MB/mm^2. TSMC not only achieved record SRAM density, but also reduced its power consumption. Because GAA nanosheet transistors have a narrower threshold voltage swing (Vt-sigma), N2 achieves a reduction in the minimum operating voltage (Vmin) of about 20 mV for high-current (HC) macros and a 30–35 mV reduction for high-density macros ( HD) compared to FinFET based designs. These improvements enable stable SRAM read and write functionality down to approximately 0.4V while ensuring robust yields and reliability.

In addition to new transistors, TSMC's N2 uses all-new middle-of-line (MoL), back-end-of-line (BEOL), and far-BEOL cabling to reduce resistance by 20% and improve power efficiency to improve. N2's MoL now uses barrier-free tungsten wiring, which reduces the vertical gate contact (VG) resistance by 55% and increases the ring oscillator frequency by approximately 6.2%. Additionally, the first metal layer (M1) is now created in one EUV exposure pass, followed by a single etch step (1P1E), reducing complexity, reducing the number of masks and improving the overall efficiency of the process. According to TSMC, using EUV 1P1E for M1 reduces standard cell capacity by almost 10% and saves multiple EUV masks. In addition, N2 reduces the resistance of metal (My) and via (Vy) by 10%.

Additional features of N2 for HPC applications also include Super High Performance MiM capacitors (SHP-MiM), which provide a capacitance of approximately 200 fF/mm² and achieve higher maximum operating frequencies (Fmax.) by reducing transient voltage drop ) contribute.

Finally, TSMC's N2 technology features a new Cu-RDL option with flat passivation and TSVs designed for face-to-face and face-to-back 3D stacking with a SoIC bond pitch of 4.5 μm is optimized to become a usable feature for AI, HPC and even mobile designs, according to TSMC.

TSMC is expected to begin production of its N2 process technology in the second half of 2025.