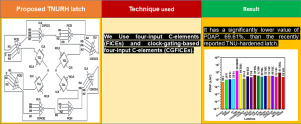

Since the technology node is further scaled by transistors, integrated circuits are more susceptible to multiple node upset (MNU), such as the double node disorder (DNU) and the triple-knot disorder (TNU). This paper presents a new 45-NM-CMOS triple-node node disorder bar (TNURH) for high-performance applications. The lock consists of transmission gates (TGS), four input C elements (FICES) and bargating-based four input C elements (CGFices). The proposed latch can repeat itself from knot upsets such as a single grading upset (snus), double-node upsets (DNUS) and triple-node-upsets (tnus). According to the simulation results, the proposed TNURH locking improves the performance results in relation to average performance, DQ delay, CLK-Q delay, power delay (PDP), product and electricity delay area product (PDAP) up to 37.75%, 23.56%, 52.94%, 36.17%and 69.61%and 69.61%. In addition, the variations of the process, voltage and temperature (PVT) and the Montecarlo (MC) simulations show that the proposed TNURH -LATCH treats the variations effectively.

High-performance and robust triple node irritation radiation hardened locking design