What you can look forward to: The storage industry is known for its conservative approach, favoring incremental improvements over revolutionary changes. But as we look towards the end of the decade, it is likely that the world will see the emergence of monolithically stacked 3D DRAMs. The only outstanding questions are what it will look like and when it will be ready for mass production.

While flash memory has made significant advances in capacity through monolithic 3D processing, DRAM has faced challenges in achieving a similar 3D architecture. The main obstacle was the need for a sufficiently large means of storing charge, typically in the form of a capacitor.

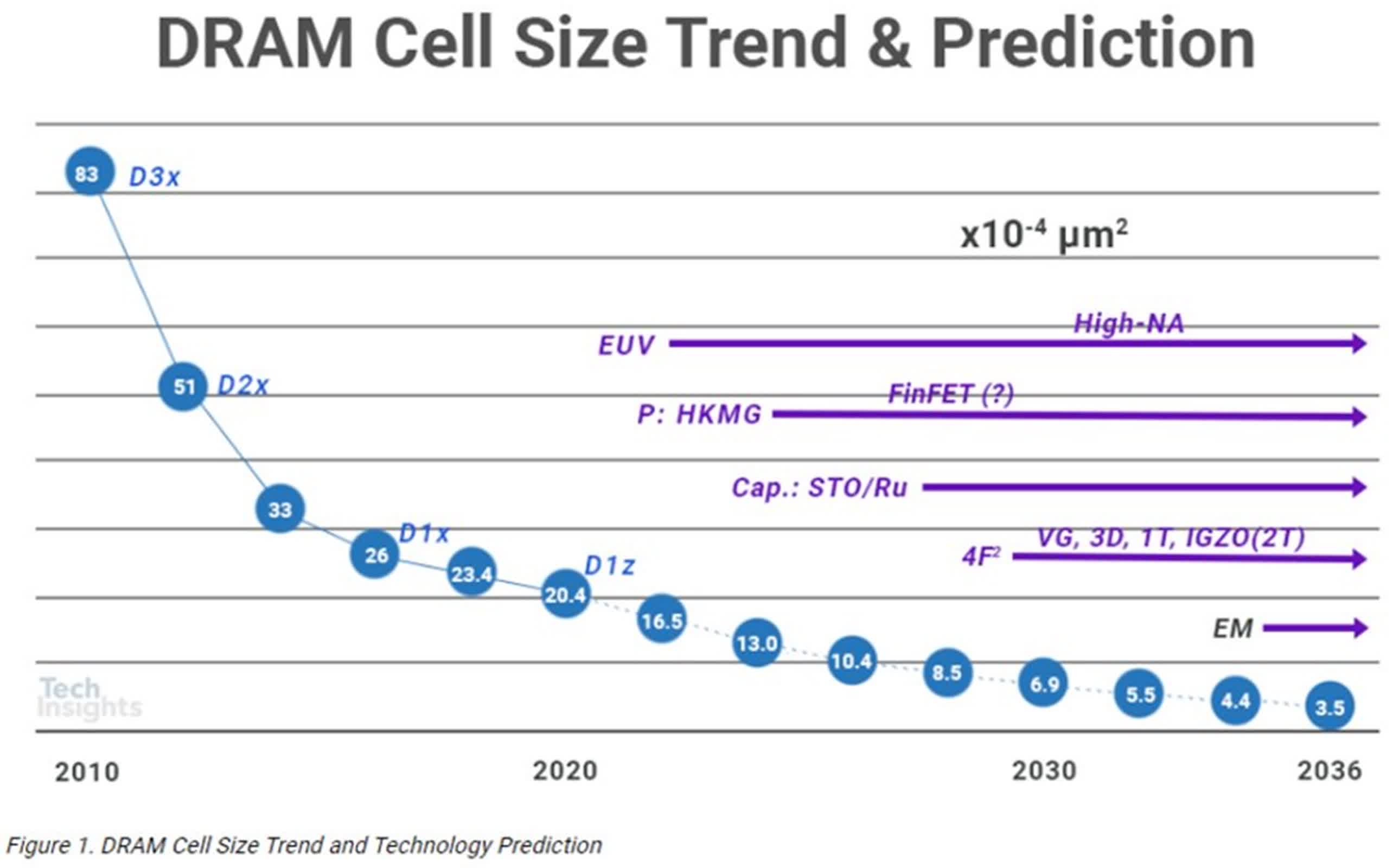

The simplest approach to increasing data storage on a single-layer DRAM chip is to reduce the cell size. However, the vertical capacitor in traditional DRAM designs creates very thick layers, making stacking difficult. To solve this problem, some efforts focus on arranging the capacitors horizontally, while others aim to eliminate the capacitor altogether.

“DRAM is following in the footsteps of NAND by evolving in three dimensions to build more memory per unit area,” said Benjamin Vincent, global senior manager of semiconductor processes and integration at Lam Research. “This is good for the industry because it pushes the technological boundaries for memory and because more bits per square micrometer leads to lower production costs.”

It is important to note that 3D DRAM can refer to two different concepts. One of them is already in production: High-Bandwidth Memory (HBM). However, HBM is a stacked chip memory and not a monolithic chip like 3D NAND flash.

The development of a monolithic 3D DRAM chip could provide an immediate boost if deployed in the HBM architecture, Daryl Seitzer, principal product manager for embedded memory at Synopsys, told Semiconductor Engineering. “If commercially viable 3D DRAM becomes available and chip stacking challenges such as thermal management are further addressed, this would be good news for HBM vendors as it introduces improvements in storage density and power efficiency that impact data centers and AI applications will impact,” he said.

One approach to optimizing DRAM cells is to shrink feature sizes using advanced lithography techniques. According to Daniel Soden, business development manager at Brewer Science, the latest steps to reduce footprint are EUV patterning compared to traditional ArF SADP and SAQP processes for cutting-edge 2D DRAM.

Samsung is working on a new cell architecture that should achieve an area efficiency of 4F2 (where F is the minimum structure size). This design uses a vertical channel transistor and switches from the current 6F2 cell to the 4F2 cell. However, construction requires new materials, including ferroelectrics, and high precision.

Another promising direction is to lay the capacitor on its side to create thinner, stackable layers. Lam Research has proposed several ideas to achieve this, including flipping the cell, moving the bitline, and using gate-all-around transistors (GAA). “Etching and deposition experts may be shocked at what our simulations suggest,” Vincent said. “In our architecture, for example, trenches with critical dimensions of 30 nm and a depth of 2 µm are considered etched and filled.”

Researchers are also exploring capacitor-less DRAM designs. One alternative involves gate-controlled thyristors, while another uses a floating body similar to the floating gate used in flash memories. Neo Semiconductor has proposed a commercial technology that uses a double-gated floating-body cell. “Simulations suggest this mechanism can increase capture margin and data retention,” said Andy Hsu, CEO and co-founder of Neo Semiconductor.

While these advances are promising, it is important to note that 3D DRAM is not just around the corner. Any current efforts will require many years of development and evaluation before achieving commercial impact. “New architectures are always more challenging than implementing existing methods,” said Soden.